LEON-RTG4

Introduction

The GRLIB IP library has support for Microsemi RTG4 devices. This support consists of a techmap layer that wraps RTG4 specific technology elements such as memory macros and pads. GRLIB also contains a template design for the RTG4 Development Kit, bridges that allow to use the Microsemi FDDR memory controller and SerDes IP together with a LEON/GRLIB system, and infrastructure that automatically builds project files for Libero SoC. More information about GRLIB and our IP cores is available on the SoC library page.

Example designs

We provide prebuilt bitstreams of the Microsemi RTG4 Development Kit LEON3 and LEON4 template design. These bitstreams are intended for evaluation of software running on a LEON3 or LEON4 SoC implemented in RTG4. To evaluate these designs, the following items are required:

- Microsemi RTG4 Development Kit FPGA board

- Workstation with GNU/Linux or Microsoft Windows

- Microsemi software to program FPGA

- Bitstream, available further down on this page

- GRMON2 or GRMON3 debug monitor - The GRMON3 evaluation version supports LEON-RTG4-EX from version 3.0.6

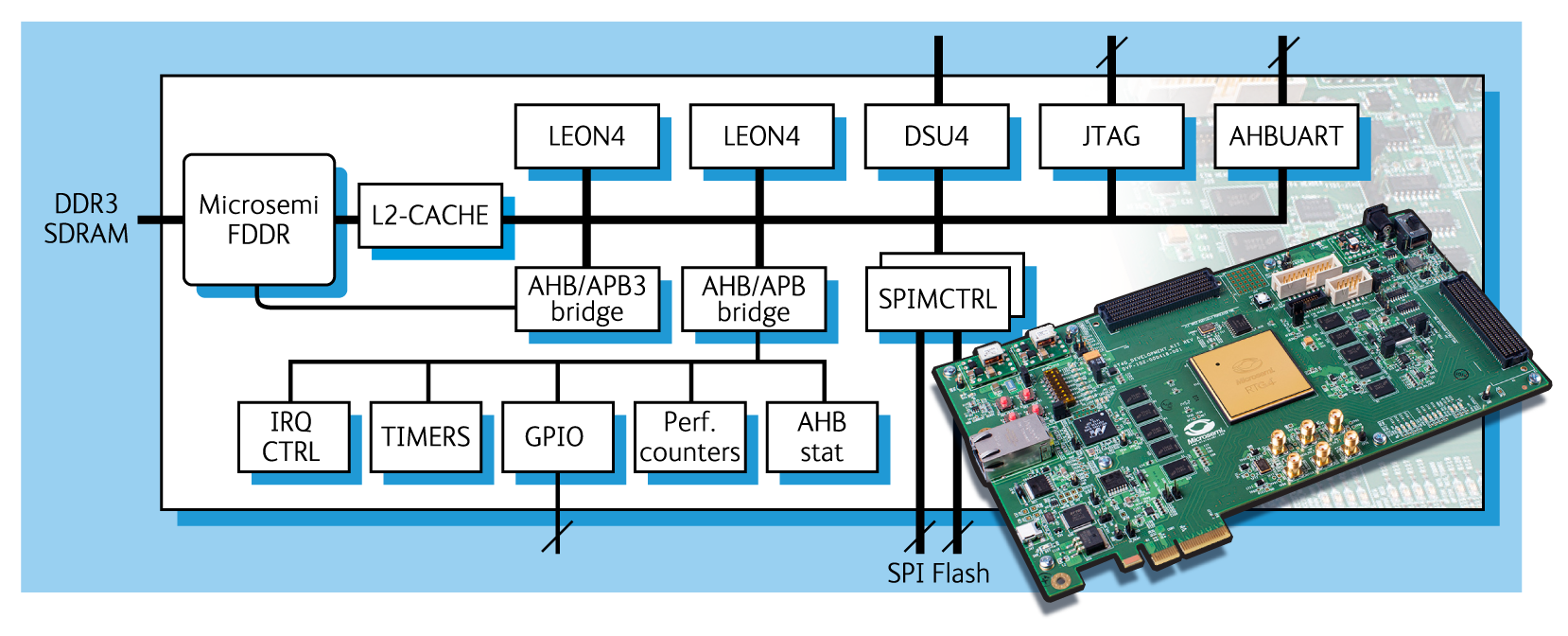

The example design range is called LEON-RTG4-EX and includes the following IP cores:

- LEON3FT and LEON4FT multicore systems with 16 KiB instruction cache and 16 KiB data cache. The processors are also implemented with MMU and FPUs.

- LEON Debug Support Unit

- Bridge for Microsemi FDDR DDR3 SDRAM controller

- SPI Flash memory controller for boot-ROM

- Interrupt controller for 15 interrupts

- Timer module with two 32-bit timers and watchdog

- UART with FIFO

- General purpose I/O port

Further documentation can be found in the user's manual below.

- LEON-RTG4-EX User's Manual (updated 2018-05-08)

- Latest version of LEON-RTG4-EX bitstream package (updated 2018-05-08)