Status:

Available

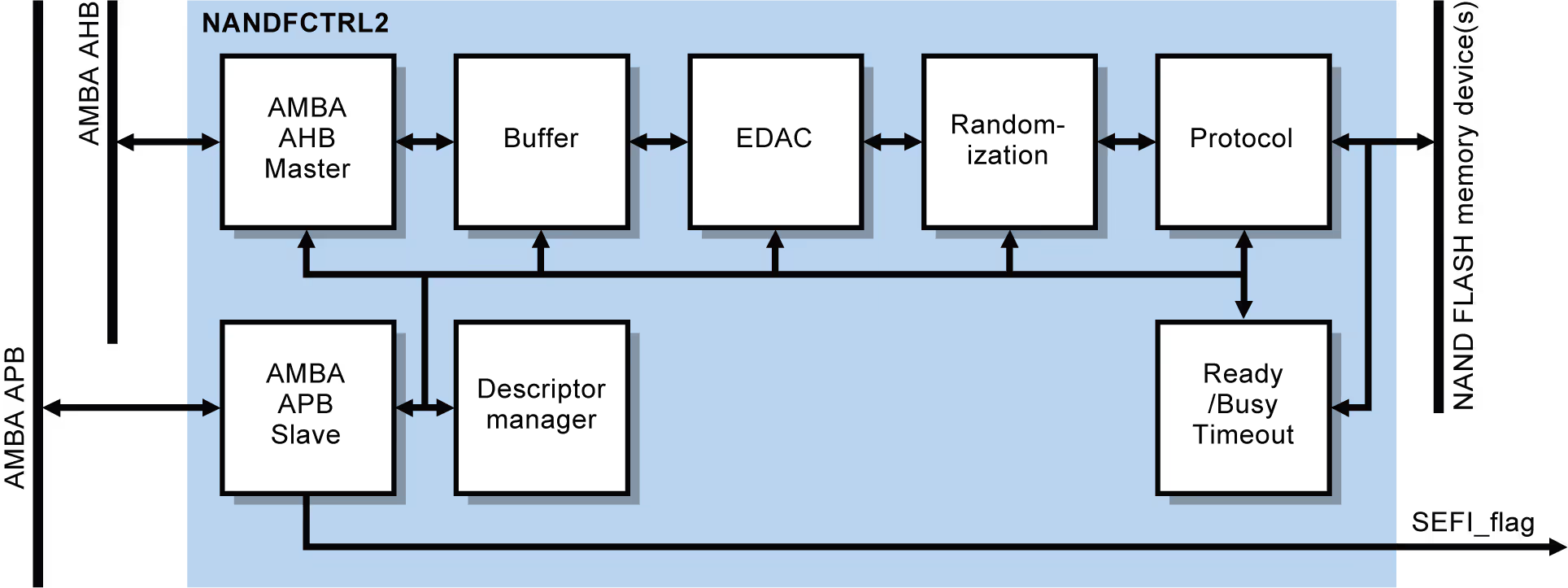

NANDFCTRL2 is a VHDL IP core implementing a NAND flash memory controller designed to operate with ONFI 4.0 devices and providing DMA transfers to and from the NAND flash memory.

The memory controller is designed to operate with ONFI 4.0 flash memory devices and provides DMA transfers to and from the memory.

The core is suitable for users who want to include NANDFCTRL2 in products and is suitable for both ASIC and FPGA implementations.

The IP is suitable for SLC-based flight-grade Raw NAND Flash interfaces, with the exception for the flight assurance related to the FPGA PHY implementation.

Future implementations are pending customer demands and include hardware LDPC ECC for supporting MLC and TLC modes.

NANDFCTRL2 supports the Frontgrade NAND memory UT81NDQ512G8T in SLC mode.

NANDFCTRL2 has been tested with the UT81NDQ512G8T, the 69F256G16, and the 3DFN128G08US8761 NAND flash memories.

ONFI 4.0 support

Other features

File

Category

Revision

Date

Access

Data sheet and user's manual

2025.2

2025-10-30

Free download

Password/

Contact us

Data sheet and user's manual

1.0

2023-09-01

Free download

Password/

Contact us

Data sheet and user's manual

1.0

2023-09-01

Free download

Password/

Contact us