We are a world leader in embedded computer systems for harsh environments, with footprints in many parts of the solar system.

We provide the full ecosystem to support digital hardware design for mission critical System-on-a-Chip solutions. The IP cores and development tools support processors based on the SPARC and RISC-V architectures. In addition to this, a number of standard components are available.

Ready to be challenged?

Are you curious about starting a new engaging role, at a world-leading company that works towards European Space Agency and NASA? Then this is your opportunity. We are continuously looking for experienced hardware and software engineers. We welcome your application!

Access our career page or contact us through career (at) gaisler.com.

SPARC or RISC-V? LEON or NOEL-V?

Ever wonder which microprocessor to use in your space system design?

Check out this white paper which discusses the differences between LEON/SPARC and NOEL-V/RISC-V architectures. The paper describes our past and ongoing component development and explains the rationale for some architectural design choices for future roadmap products. Included herein are trends in the Space industry that are driving key new features example application use-cases and tradeoffs from a software perspective of a legacy LEON/SPARC design vs. a new RISC-V architecture.

Access the white paper

RISC-V Processor Model - NOEL-V

The NOEL-V is a synthesizable VHDL model of a processor that implements the open RISC-V architecture from the RISC-V International organization.

This is the first released model in the RISC-V product line of processors. Seven different configurations are now available for NOEL-V, ranging from a tiny 32-bit version to a 64-bit high performance version. NOEL-V complements the LEON line of processors. Click here for more information.

Rad-Hard Dual-Core Processor

Dual-Core LEON3-FTGR712RC Radiation-hard Dual-Core LEON3-FT Processor, 200 MIPS, 200 MFLOPS |

|

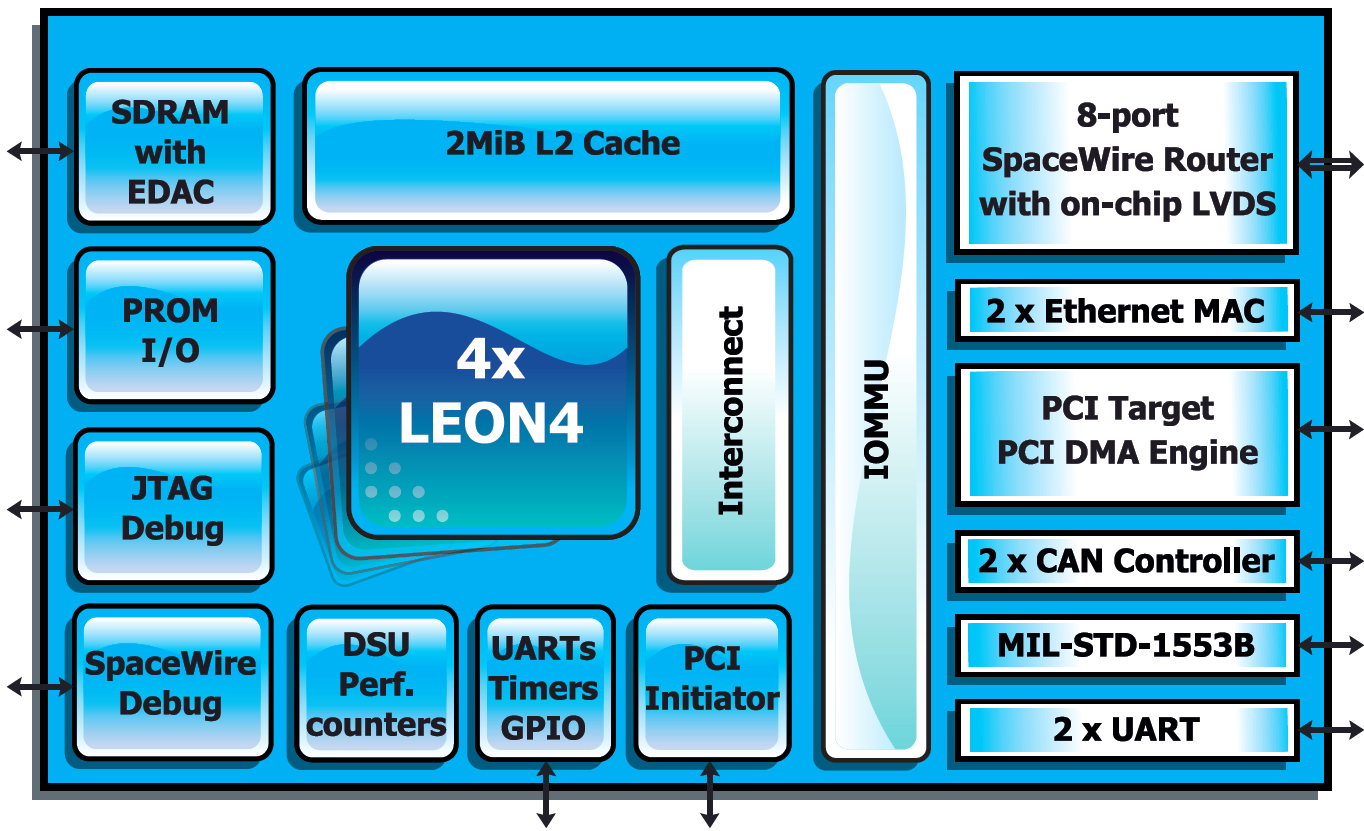

Rad-Hard Quad-Core System-on-Chip

Quad-Core LEON4-FTGR740 Radiation-hard Quad-Core LEON4-FT Processor, 1000 MIPS, 1000 MFLOPS, QML-V/QML-Q |

|

GR740 CG625 |

The GR740 component has received QML-V and QML-Q quality certification by DLA in Q2 2022. Access the GR740 SMD 5962-21204.

Rad-Hard Quad-Core System-on-Chip - Plastic

Quad-Core LEON4-FTGR740-PBGA Plastic Radiation-hard Quad-Core LEON4-FT Processor, 1000 MIPS, 1000 MFLOPS |

Get updates via e-mail

Please use this form to sign up for our Newsletter.

Latest Releases

| NOEL-V processor model GRLIB IP Library 2024.2-b4293 GR712RC user's manual 2.16 GR712RC data sheet 2.5 GR740 user's manual 2.6 GR716A data sheet 3.2 GR718B user's manual 3.8 GR716B data sheet 0.7 |

GRMON3 Debug Monitor 3.3.11 GRMON2 Debug Monitor 2.0.99 TSIM3 LEON Simulator 3.1.11 TSIM2 LEON/ERC32 Simulator 2.0.66 BCC Bare-C Compiler 2.3.0 RCC RTEMS Compiler 1.2.25, 1.3.2 VxWorks 7 support for LEON VxWorks 6.9 support for LEON |

LEON and NOEL FPGA Evaluation Designs

|

LEON/GRLIB examples for Lattice Certus/Pro-NX-RT |

Frontgrade Gaisler Awarded ESA Contract to Qualify Spacecraft Avionics Microcontroller for Flight

The European Space Agency (ESA) has awarded us a contract under the ARTES Core Competitiveness programme to qualify the GR716B microcontroller for flight.

Read the press release.

RISC-V Summit Europe 2024

As a RISC-V strategic member and a Gold sponsor, we can't miss the RISC-V Summit Europe 2024! Join us at booth # 9 to discover how our resilient processors can power your projects.

Access the event.

4S Symposium

We are exhibiting at the Small Satellites Systems and Services Symposium (4S), organized by ESA and CNES. Join us at booth 44 to discover our latest technologies!

Access the event.

Frontgrade Gaisler Leads the Way in RISC-V Processor Development for Space Applications

We have been awarded a European Space Agency - ESA contract to design a new RISC-V International compliant processor IP core tailored to meet the requirements of microcontrollers for the space industry.

Read the press release.

BrainChip and Frontgrade Gaisler to Augment Space-Grade Microprocessors with AI Capabilities

We announced our collaboration with BrainChip to explore the integration of BrainChip’s Akida™ neuromorphic processor into our next generation fault-tolerant, radiation-hardened microprocessors.

Read the press release.

GR740-MINI

The GR740-MINI evaluation board is a compact evaluation platform for the GR740 quad-core LEON4FT and the CertusPro-NX-RT FPGA. Read more

Frontgrade Gaisler's Microprocessor Empowers Multiple Computer Systems in JAXA's H3 Launch Vehicle

Gaisler's American Tour 2024

This year Frontgrade Gaisler will embark on a grand tour across North America, visiting, presenting and exhibiting at major space events, to connect with our valued customers. Don't miss the opportunity to meet us in person at these events. Swing by our booth to discover the latest innovations and solutions we have in store for you. We are extending an invitation to schedule a meeting through your local sales representative. Whether it's at the conference or at your own premises nearby, we're eager to have meaningful discussions tailored to your specific needs.

Collaboration with Klepsydra AI to expand microprocessing versatility in space missions

We have together with Klepsydra Technologies (AI), a leading provider of artificial intelligence (AI) software solutions, announced an initiative to adapt AI algorithms to run on microprocessors used in space missions. This effort is part of a contract recently awarded to Klepsydra by the European Space Agency - ESA to port Klepsydra AI to Frontgrade Gaisler’s GR740 and NOEL-V processors, enabling high performance and reliable AI applications.

Read the press release.

Follow us on Twitter and LinkedIn

Follow us on Twitter and LinkedIn.

More news...