Status:

Available

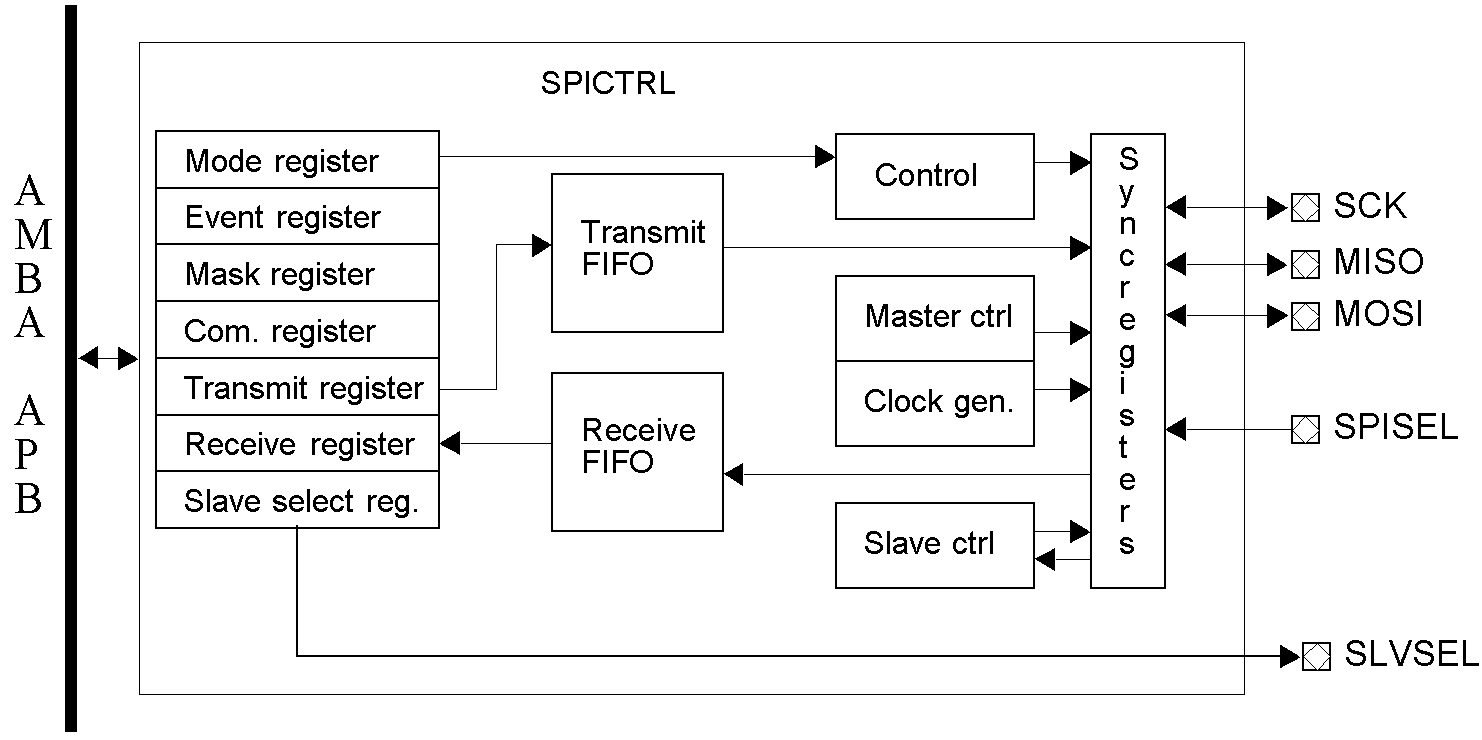

The SPICTRL provides a link between the AMBA APB bus and the Serial Peripheral Interface (SPI) bus. Through registers mapped into APB address space the core can be configured to work either as a master or a slave.

The core provides a link between the AMBA APB bus and the Serial Peripheral Interface (SPI) bus. Through registers mapped into APB address space the core can be configured to work either as a master or a slave.

File

Category

Revision

Date

Access

Data sheet and user's manual

2025.2

2025-10-30

Free download

Password/

Contact us